빠른 CPU를 만드려면 높은 클럭 속도, 멀티코어, 멀티스레드를 지원하는 CPU를 만드는 것도 중요하지만, CPU가 놀지 않고 시간을 알뜰하게 쓰며 작동하게 만드는 것도 중요하다. 이번 글에선 명령어를 동시에 처리해 CPU는 한시도 쉬지 않고 작동시키는 기법인 명령어 병령 처리 기법(ILP. Instruction-Level Paralleism)을 알아볼 것임

1. 명령어 파이프라이닝

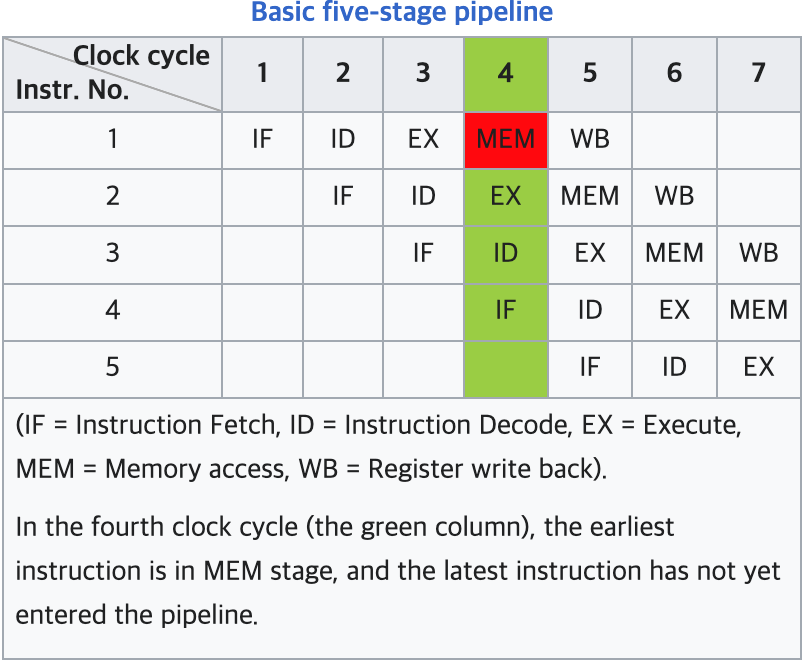

- 하나의 명령어가 처리되는 전체 과정은 일반적으로, 명령어 인출 → 명령어 해석 → 명령어 실행 → 결과 저장

- 같은 단계가 겹치지만 않는다면, CPU는 마치 공장 생산 라인처럼 명령어들을 명령어 파이프라인에 넣고 동시에 처리할 수 있음

- 파이프라인 위험 - 파이프라이닝이 높은 성능을 가져오지만, 특정 상황에서 실패하는 경우가 있음

- 데이터 위험

- 명령어 간 '데이터 의존성'에 의해 발생함. 어떤 명령어는 이전 명령어를 끝까지 실행해야만! 비로소 실행할 수 있는 경우가 있음

- 명령어 1: R1 ← R2 + R3

- 명령어 2: R4 ← R1 + R5

- 명령어 간 '데이터 의존성'에 의해 발생함. 어떤 명령어는 이전 명령어를 끝까지 실행해야만! 비로소 실행할 수 있는 경우가 있음

- 제어 위험

- 주로 분기 등으로 인한 '프로그램 카운터의 갑작스러운 변화'에 의해 발생함

- 기본적으로 프로그램 카운터는 '현재 실행 중인 명령어의 다음 주소'로 갱신됨. 하지만 프로그램 실행 흐름이 바뀌면, 프로그램 카운터 값에 갑작스러운 변화로 미리 처리 중이었던 '현재 실행중인 명령어의 다음 주소인 명령어들'은 아무 쓸모가 없어짐

- 이때 사용하는 기술 중 하나가 분기 예측. 분기 예측은 프로그램이 어디로 분기할지 미리 예측한 후 그 주소를 인출하는 기술

- 구조적 위험(자원 위험)

- 명령어들을 겹쳐 실행하는 과정에서 서로 다른 명령어가 동시에 ALU, 레지스터 등과 같은 CPU 부품을 사용하려고 할 때 발생함

- 데이터 위험

2. 슈퍼스칼라

- 명령어 파이프라인 하나 - 공장 생산 라인을 한 개 둠

- 명령어 파이프라인 여러개(슈퍼스칼라) - 공장 생산 라인을 여러 개 둠

- 이론적으론 파이프라인 개수에 비례해 프로그램 처리 속도가 빨라지지만, 파이프라인 위험 등의 예상치 못한 문제가 있어 실제로는 비례해 빨라지지는 않음

- 한 개의 파이프라인을 사용할 때보다 데이터, 제어, 자원 위험을 피하기 까다롭기 때문에 슈퍼스칼라 방식을 차용한 CPU는 파이프라인 위험을 방지하기 위해 고도로 설계해야 함

3. 비순차적 명령어 처리(OoOE. Out-of-order excution)

- 명령어들을 순차적으로 실행하지 '않는' 기법. 합법적인 새치기

- 이따금씩 어떤 명령어는 곧바로 처리되지 못하기도함. 모든 명령어를 순차적으로만 처리한다면 이런 상황에선 멈춰버리게됨

- 명령어 중에는 데이터 의존성이 전혀 없는, 순서를 바꿔 처리해도 수행 결과에 영향을 미치지 않는 것들이 있음

- 이런 명령어들을 순서를 바꿔 처리하면, 명령어 파이프라인이 멈추는 것을 방지할 수 있음

'computer science > computer architecture' 카테고리의 다른 글

| [오늘 CS] 컴퓨터 구조 - 메모리(RAM) (0) | 2024.04.30 |

|---|---|

| [오늘 CS] 컴퓨터 구조 - CISC와 RISC (0) | 2024.04.24 |

| [오늘 CS] 컴퓨터 구조 - CPU 성능 향상을 위한 설계 기법 (1) | 2024.04.23 |

| [오늘 CS] 컴퓨터 구조 - 명령어 사이클과 인터럽트 (0) | 2024.04.03 |

| [오늘 CS] 컴퓨터 구조 - 레지스터 (1) | 2024.04.02 |